|

|

|

|

SPERRY

Univac AN/UYK-7 (V)

computer

set

Developed and designed 1968, based on

an announcement by the US Ministry of Defense/ NAVY to equip warships

with digital computers. Other applicants included IBM and Honeywell.

However, SPERRY UNIVAC won the framework contract.

The displayed unit was part of a German NAVY data center located in

Wilhelmshaven, Germany. Two of the seven moduls inside are marked with

"Rheinland Pfalz", which was a class F122 fregatte in the German Navy

(Bundesmarine) stationed in Wilhelmshaven.

The AN/UYK-7 ("Yuckseven") computer set became the standard Navy ship

computer. Because of the multi-processor capability it was used on all

types of ships and came in different configurations. Originally, the

chassis with serial A-1332 was part of a three-bay installation,

consisting of 2 CPUs, 2 I/O-Controllers and a memory bank.

The UYK-7 computer system was previously also installed on the German

class F103 warships (Lütjens-Klasse) at the Federal

German Navy.

It took me a while to reconfigure this unit to a standard one-bay

system. Three types of bus-systems - an instruction-bus, an

operand-bus, and an I/O-bus, each consisting of 52 signal-drilled lines

- have to be maintained and must be electronically terminated inside

the chassis. In addition, some signalling lines needed to be resolded

to say: there is now no other system besides you, and this is OK.

Each of the seven modules have its own terminal boards at the front

with up to 200 signal points for testing - a very comfortable selection

for troubleshooting. Furthermore, there is a maintenance console with

several bulbs and switches on top, designed in the classic black UNIVAC

manner to examine each step in a process and the status of the overall

82 CPU registers.

It is very interesting to see the many blinking lights during a simple

operation, for example the addition of two numbers; it costs attention

and focus to maintain an overview over the registers during the process

steps.

What seems very complicated is, however, internally a very fine and

well documented architecture. The arithmetic registers are with a few

exceptions implemented with NAND gates. UNIVAC had its own integrated

circuit design, and the contractors were MOTOROLA, FAIRCHILD, and

RAYTHEON. There is a good article written by Larry D. Bolton "The

UNIVAC 7901000-series Integrated Circuits" that covers this topic.

The UYK-7 has its own philosophy, oriented on the heavy I/O-traffic on

a warship for data collection, visualization and data calculation for

sonar, fire leading and target radar, display units and control of the

weapon systems. Therefore, the AN/UYK-7 has a very complex

IO-Controller with its own registers and its own comand set - the

I/O-bus has always the highest priority in all steps and operations.

Remarkable is the so called IO-adapter with 32 connectors, two each for

input and output. Input/Output is done with the NTDS (Naval Tactical

Data System), a very special and ornate protocol with tight

tolerances for pulse times, which cannot be compared with any interface

known in commercial environments.

Note the BATTLESHORT switch at the operator console.

It was intended to shorten an internal signalling system, which

normally shuts off the computer in case of overtemperatur or

overcurrent. When pressed, calculating still goes on.

I aquired and restored this unit with a few spares and a complet set of

original paper documentation in 2024.

See the full story below (in German language, because the museum is

located in Germany):

|

SPERRY

Univac AN/UYK-7 computer

set: front view with maintenance console on top, USA, St. Paul, ca.

1974.

|

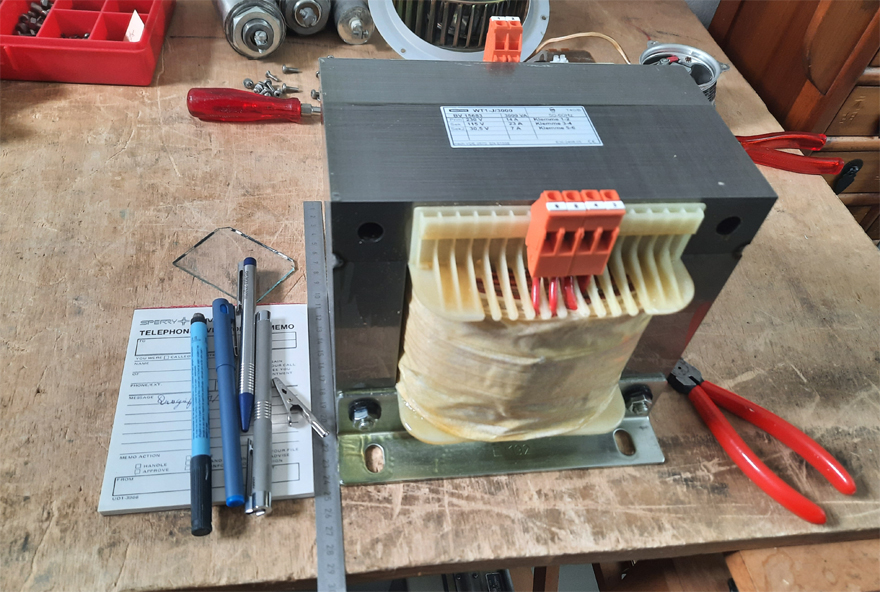

Als echter Amerikaner und echter Schiffsrechner wird der AN/UYK-7

computer an

einem 3Ph-115V-400Hz Stromanschluss betrieben - eine auf dem (europäischen) Festland

nur schwerlich

zugängliche Art der Spannungsversorgung. Wie

schließt man einen solchen Rechner an und bringt ihn in

Betrieb?

Da im Netzteil sekundärseitig nur zwei Spannungen (-150V,

-38V) die Grundlage

für alle weiteren Schaltnetzteile in den Modulen bilden und

die 400 Hz Frequenz nicht taktgebend ist, war für dieses

Exemplar mit Ser. No. 1332 ein Umbau auf 1Ph-230V-50Hz

möglich; den Transformator hat die Firma Walcher gewickelt.

Betrieben mit entsprechenden Filtern und einer

Einschaltverzögerung zeigt der Rechner nach erfolgreicher Inbetriebnahme eine Gesamtleistung von

rund 3000 Watt.

|

Eigens für den AN/UYK-7 beauftragter Transformator der Firma

WALCHER, 2024.

|

Das Chassis beherbergt neben der Einschaltlogik für die

Elektrik einen Doppellüfter (ROTRON), das fest verdrahtete

Backplane, ein Operator Panel und mit einem I/O-, einem Instruction-

und einem Operand-Bus insgesamt drei Bussysteme zu je 52 verdrillten

Adern. Jede Ader ist an ihren Enden jeweils mit 100 Ohm abgeschlossen

und mit 2,5 Volt vorgespannt - eine vergleichsweise

aufwändige, aber auch sehr resiliente und stabile Architektur.

Mit den Bussystem lassen sich auch je nach Steckplatz die

Prioritäten der einzelnen Module hardware-seitig steuern.

|

SPERRY Univac: AN/UYK-7 computer set cabeling. Ausschnitt unten. USA,

ca. 1974

|

Nach Austausch der 115V-Relais und des -Lüfters, dem Wechsel der

primärseitigen

Signallampen auf 230V Spannungsversorgung im Gestell, sowie die

Ausrichtung

des Gehäuses und des Netzteil-Einschubs auf die einphasige

Sekundärspannung

können die vier "Switching Regulators" im Netzteil in Betrieb

genommen werden. Diese vier Haupt-Schaltnetzteile wandeln die

-150V-Spannung in eine interne -90V-Spannung, die widerum Grundlage

für

die Schaltnetzteile in den einzelnen Rechnermodulen ist.

Elektronisch sind die Schaltnetzteile (von 1968) noch von anderer

Bauweise als heutige (2024) Modelle: Die Eingangspannung wird mithilfe

eines Oszillators und zwei Gegentakt- Leistungstransistoren gepulst

und auf einen Transformator gegeben, sekundärseitig

gleichgerichtet und abschließend gesiebt und stabilisiert.

Ein

Regelkreis bestimmt die Impulsweite der primärseitigen Pulse

und

somit der Stabilität der Spannung bei sich ändernder

Last.

Für damalige Verhältnisse

sind der Wirkungsgrad und die Leistungsfähigkeit von bis zu

800

Watt bei vergleichsweise geringen Ausmaßen beachtlich.

|

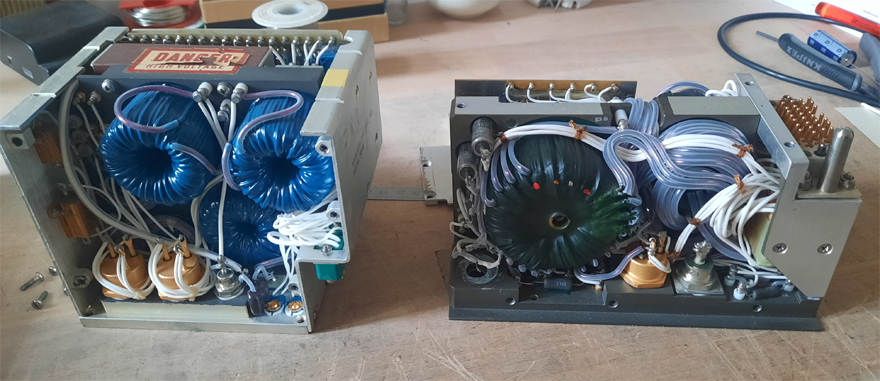

SPERRY Univac: AN/UYK-7 computer set: -90V Schaltnetzteil

(links) und das Netzteil für die CPU. USA, ca. 1974.

|

Jeder der sechs Rechnereinschübe verfügt

über sein

eigenes Netzteil (Bild oben, rechts), das die -90V Spannung

auf bis zu sechs

Arbeitsspannungen (+5V, +15V, +6V ...) wandelt. Die

Ringkertransformatoren sind äußerst

kompakt und

leistungsfähig: in den +5V - Lines fließen insgesamt

bis zu

45A.

|

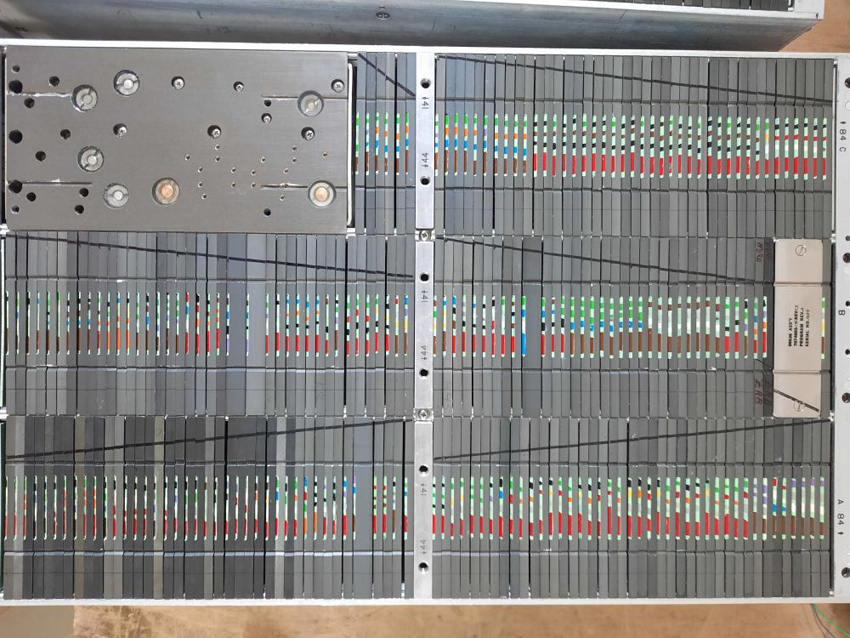

SPERRY Univac: AN/UYK-7 computer set: Central Processor Unit. USA,

ca.1974.

|

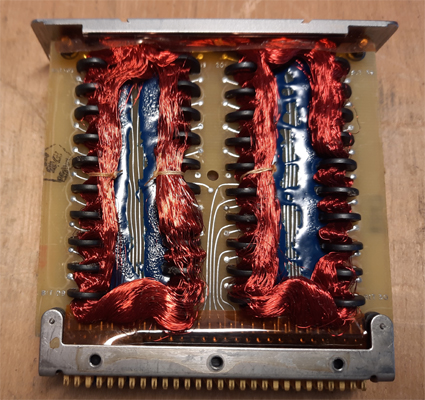

Auf dem Bild oben ist die Central Processor Unit bei abgenommenem

Kühldeckel zu sehen. Auf rund 200 Steckkarten ist die gesamte

Logik,

die über 80 Register, die Steuerung und die Arithmetik

untergebracht. Oben links das

CPU-Schaltnetzteil. In der Mitte rechts ist (silbern) das Non

Destructive Readout (NDRO) zu erkennen - ein Fädelspseicher

mit

512 Worten, der neben den Ladeprogrammen auch einige

Prüfroutinen

enthält für CPU, Busse, IO-Controller und den

Speicher

enthält.

|

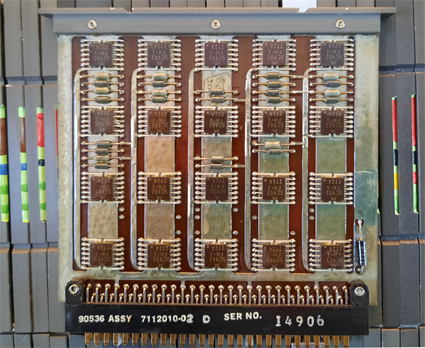

SPERRY Univac: AN/UYK-7 computer set: Baugruppe 2010 (links)

Baugruppe Fädelspeicher NDRO (rechts). USA, 1977.

|

Bild oben zeigt eine typische Steckkarte (Typ 7112010): Ein Teil des

mit

Flip-Flops (MOTOROLA SC901) aufgebauten Arithmetischen Registers. Auf

dem

Bild rechts ist der Fädelspeicher zu erkennen: 512 x 32 Bit

Worte, die in

diesem Falle konkret zwei Ladeprogramme - eines für ein UNIVAC

1840 Bandlaufwerk, das andere für eine Festplatte - und einige

Diagnostik-Routinen persistent hält.

|

SPERRY Univac: AN/UYK-7 computer set: |

Die auch von ganz frühen UNIVAC-Rechnern bekannte Maintenance

Console mit etlichen Schaltern und Lämpchen ist für

den

AN/UYK-7 computer in obigen Bild

im Ausschnitt abgebildet. An dieser Konsole lassen sich Programme

laden, die Inhalte der Central Memory Register anzeigen und

verändern, der gesamte

Programmablauf steuern, Stoppbedingungen einlegen und

Programmabläufe bis in jede Arithmetische Phase einsehen. Die

Console ist unterteilt in den Teil für den IO-Controller

(oben) und den unteren, größeren Teil für

die Central Processing Unit.

(Angezeigt wird im Bild oben ein aus dem Speicher in das 32-Bit

U-Register eingelesener Test-Patter bestehend aus im Wechsel acht

Nullen und acht Einsen.

Wie "tickt" dieser Rechner ?

Der SPERRY UNIVAC AN/UYK-7 ist gemessen an seinen Zeitgenossen Ende der

1960er, Anfang der 1979er Jahre eine vergleichsweise komplexe,

vielschichtige Maschine. Das mag an seinem Einsatzgebiet als

Marinerechner mit entsprechend anspruchsvollem Lastenheft liegen, aber

auch daran, dass kaum ein anderes Unternehmen eine derart tiefe und

langjährige Erfahrung im Digital-Rechnerbau hatte wie SPERRY

UNIVAC (SPERRY hatte 1955 durch Übernahme von REMINGTON RAND

auch die Computersparte UNIVAC übernommen; UNIVAC setzte sich

u.a. aus einem dem ENIAC-Projekt hervorgegangenen Team

zusammen).

In der mir überlieferten Geschichte gilt der SPERRY UNIVAC

AN/USQ-20 (auch UNIVAC 1206, NTDS oder CP642A) als der

Vorgänger des AN/UYK-7; zumindest waren AN/USQ-20s auch bei

der Bundesmarine im Einsatz und wurden dann durch AN/UYK-7 Rechner

abgelöst. Aus der "SPERRY

UNIVAC COMPUTER GENEALOGY" geht der

CP855 von 1965 (auch unter der Bezeichnung UNIVAC 1230) als technischer

Vorläufer hervor.

Beide 30-Bit Systeme lassen die Konzepte und Begrifflichkeiten des

AN/UYK-7 bereits deutlich erkennen; in mancherlei Hinsicht ist der

AN/UYK-7, was seine Arithmetik und vorallem die zum Einsatz kommende

Halbleiter-Technologie angeht, aber mehr eine Neu- denn nur eine

Weiterentwicklung.

Der AN/UYK-7 ist - allein schon wegen seiner um 2 Bit erweiterete auf

32 Bit Wortbreite - nicht abwärtskompatibel, spricht aber nach

außen hin das gleiche NTDS (Narval Tactical Data System).

Der sehr umfängliche Befehlssatz für den AN/UYK-7

erfordert eine recht ausdifferenzierte Arithmetik mit entsprechend

mehrphasigem Timing.

Die untenstehenden Bilder geben einen Eindruck des Zusammenspiels:

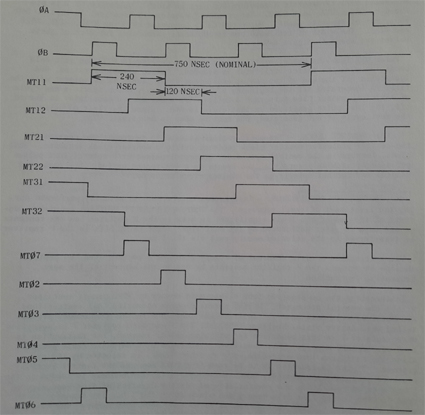

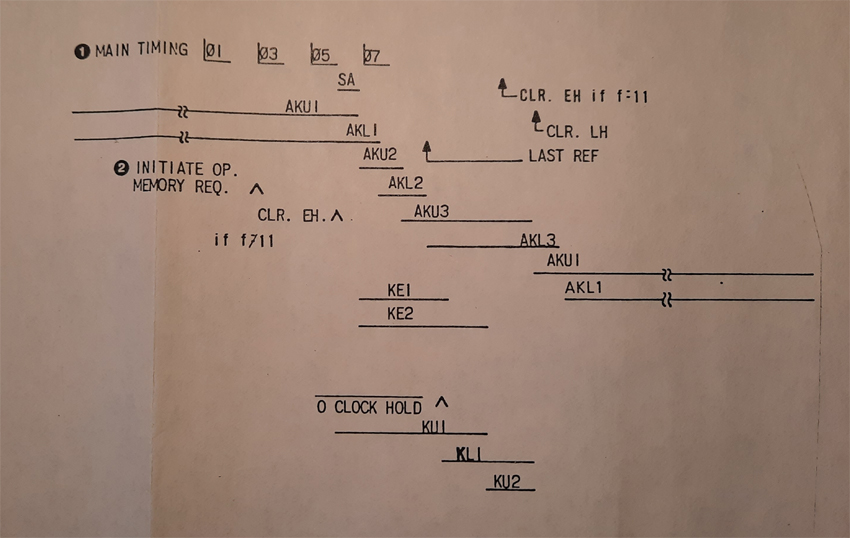

Links:

Die Takte der CPU-MasterClock werden in ein Main-Timing

(Hauptzeitsteuerung) überführt, das den gesamten

Ablauf innerhalb der CPU koordiniert. Aus der Hauptzeitsteuerung geht

auch das Signal "Start Arithmetic" (SA) hervor, das wiederum eine Reihe

weiterer Zeitsteuerimpule (AK-, K- und K*- Zeitsteuerketten)

für die interen Arithmetik initialisiert. Diese

Zeitsteuerketten sind als Ringzähler organisiert, die je nach

Komplexität des auszuführenden Befehls mehr oder

weniger weit durchgetaktet werden. Der Zustand der AK- und

K-Zeitsteuerketten werden auch auf der Maintenance Console zur Anzeige

gebracht, was ein sehr detailiertes Studium des Rechenwerks und der

Ablaufsteuerung bei einezelnen Befehlen ermöglicht.

Rechts:

Mitschnitt des Timings eines Ladebefehls (f=10) mit einem

Logik-Analyzer (HP 1630D), das auch das Zusammenspiel Bussteuerung und

Arithmetik zeigt. Die AKU-Signale sind low-active.

Main Timing 1, Main Timing 2, Main Timing 3,

AK-Timing Upper 1, AK-Timing Upper 2, AK-Timing Upper 3,

AK-Timing Upper 4,

Start Arithmetik,

Initiate AT0-Timing (Start der K-Sequenz),

Late Hold

Operate Clock Hold

Start

|

SPERRY Univac: AN/UYK-7 computer set: Main-Timing (links) und Ablauf

der AK-Timing-Chain (rechts).

|

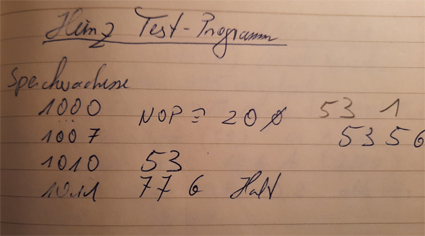

Untenstehend noch die Theorie des gleichen Befehls (f=10) aus

den Lehrgangs-Unterlagen.

Wer also sehr genau hinschaut erahnt im Vergleich mit dem Bild des

Mitschnitts Logic Analyzer den Fehler, den die reale CPU hatte: Die

AKU-Signale überschneiden sich, dürften es aber

theoretsch nicht. Es hatte am realen Rechner zur Folge, dass

die CPU bei Eintritt in die Arithmetische Sequenz Inhalte von Registern

durcheinanderwürfelte und fehlerhaft gerechnet hat (bis zu

diesem Zeitpunkt - korrekter Speicherzugriff, Befehlsholung,

Einsortieren und Interpretation des Befehls - war alles OK).

Das Problem konnte am Ende nur dadurch gelöst werden, dass dem

AN/UYK-7 ein anderer CPU-Einschub spendiert wurde (Danke

dafür), in der sich ein mit den Lehrgangsunterlagen

identisches Timing volzog :-).

|

SPERRY Univac: AN/UYK-7 computer set: Zeitdiagramm beim Befehl Lade

Akkumulator A (f=10).

|

Der AN/UYK-7 Computer ist ein Spezialist und entlang den

Anforderungen zum Betrieb auf einem Marineschiff hin konzipiert, was

sich insbesondere am Interrupt-Handling und an seinen sehr

umfangreichen I/O-Schnittstellen (mit eigenem I/O-Controller) zeigt.

Von seinem Befehlssatz her ist der Rechner aber auch ein

großer Universalist (General Purpose Computer), der es

mühelos mit anderen Rechnern aus seiner Zeit und anderen

Aufgabenstellungen aufnehmen kann.

Eine erste Programm- und Software-Studie bieten die im NDRO

hinterlegten Routinen, die nach Setzen eines Bits im Active Status

Register ausgelesen und ausgeführt werden können.

In dem hier verbauten NDRO mit der Endung -135 sind das u.a

Memory Test

location 606 - 653

entrance 607

Interface Test

location 654 - 747

entrance 655

Inspect and Change location 736 - 776

entrance 776

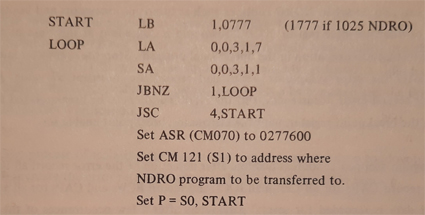

Der AN/UYK-7 kennt 130 Grundbefehle. Aller Anfang ist schwer - das

erste (eigene) Programm schrieb und erklärte mir ein ehemalger

Service-Ingenieur: Eine einfache Schleife die den Zustand eines

Schalters auf der Wartungskonsole abfragt. Das zweite selbst erstellte

Programm kopiert den Inhalt des NDRO in den Doueble Density Film Memory

(DDFM).

Die aus wenigen Zeilen bestehenden Programme lassen sich (Bit

für Bit) über die Management Console eingeben und in

32 BitBlöcken den Speicher übertragen:

|

SPERRY Univac: AN/UYK-7 computer set: Zwei (einfache) Programme

|

Was den AN/UYK7 (und Ähnliche) zu einer Ausnahme in der

Rechnerwelt macht ist zum einen seine starke Orientierung an die

Datenein- und -ausgabe. Der Ein-/ Ausgabe - Adapter (IOA) stellt 16

Kanäle zur Verfügung, wobei jeder Kanal über

eine separate Ein- und Ausgabe-Buchse verfügt. Die zweite

Besonderheit: Alle Ein- und Augabekanäle sind auf das

marine-eigene NTDS ausgerichtet - eine (bis heute) in MIL-STD-1397C

beschriebene Schnittstelle (man würde heute sagen: ein

Protokoll).

So leicht verständlich das Format auch ist - diese

Schnittstelle ist mit keiner anderen Computer-Schnittstelle auch nur

annähernd kompatibel (sprich: man kann nichts Bekanntes an den

Rechner anschließen). Es sind weder Übersetzer, noch

Adapter erhätlich oder hinreichend beschrieben.

|

SPERRY Univac: AN/UYK-7 computer set: Ein- /Ausgabe- Adapter

|

Erst etwas später fand sich für den AN/UYK-7 in der

Sammlung ein (zunächst uni-direktionaler)

Gesprächsparter: Ein UNIVAC Type 47209 NTDS Paper Tape Reader.

In einemWartungs-Koffer eingebaut ist ein eher

selten anzutreffender DIGITRONICS 2031 Lochstreifenleser untergebracht,

der innen und auf der Rückseite von UNIVAC um eine

NTDS-Schnittstelle ergänzt wurde.

|

SPERRY Univac: AN/UYK-7 computer set: UNIVAC Type 47209 Paper Tape

Reader

|

Nach der erfolgreichen Instandsetzung des UNIVAC 47209 (zum

Glück

war die Dokumentation inliegend) musste noch ein

Überspielkabel

angefertigt und ein kleines Ladeprogramm geschrieben werden.

Das erfolgreiche Einspielen eines beiliegenden Lochstreifens mit

Muster-Pattern lässt sich in diesem

Video bestaunen (mp4-Format).

Literatur/

Dokumentation

NAVSEA 0967-LP-319-4010 Technical

Manual, Volume 1, Sections 1-5, Operation & Maintenance. SPERRY

UNIVAC, September 1977.

NAVSEA 0967-LP-319-4020 Technical Manual, Volume 2, Section 6, Parts

List. SPERRY UNIVAC, September 1977.

NAVSEA 0967-LP-319-4030 Technical Manual, Volume 3, Circuit Diagram

Manual, Part 1. SPERRY UNIVAC, September 1977.

NAVSEA 0967-LP-319-4040 Technical Manual, Volume 4, Circuit Diagram

Manual, Part 2. SPERRY UNIVAC, September 1977.

PX 6503 NDRO Program Operating Procedures. SPERRY UNIVAC, September

1973.

PX 5652E AN/UYK-7 Technical description. SPERRY UNIVAC, 1972

Test

PROGRAM

NAVSEA 0967 LP-024-5474 Part II

Supplemetary Diagnostic Test Program (paper tape)

|

| |

|

| |

| |

| Kategorien |

Computersysteme

<--

-->

|

|